DRAM output is a fundamental concept in computer architecture and memory systems. It refers to the data that a Dynamic Random-Access Memory (DRAM) chip sends out during a read operation. Understanding DRAM output is useful for students, engineers, and anyone learning how CPUs, memory controllers, and modern computing systems exchange data.

What Is DRAM Output?

DRAM output is the binary data (0s and 1s) driven onto the data bus by a DRAM module when it is read. This data appears on the DRAM’s DQ (data) pins after the correct row and column addresses are accessed and timing requirements are met.

In simple terms:

DRAM output is the information that comes out of memory when the system requests stored data.

How DRAM Output Works

A DRAM read operation follows a precise sequence before valid output appears:

- Row Address Activation (RAS)

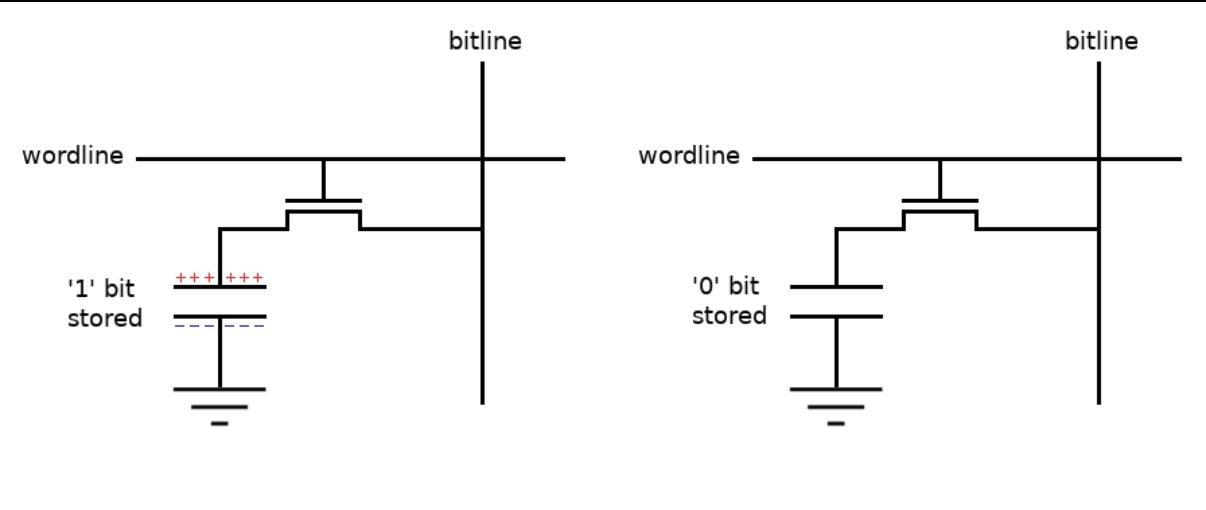

The memory controller selects a row in the DRAM array. - Sense Amplification

Tiny electrical charges stored in capacitors are detected and amplified. - Column Selection (CAS)

A specific column within the activated row is selected. - Data Output Enabled

The selected data is placed on the DQ output pins. - Valid Data Window

During this period, the DRAM output can be safely read by the controller or CPU.

Key Characteristics of DRAM Output

- Binary digital data transmitted over the memory bus

- Timing-dependent, governed by parameters such as CAS latency (CL)

- Synchronous in modern systems (DDR, DDR2, DDR3, DDR4, DDR5)

- Tri-stated (high impedance) when the memory is not actively being read

DRAM Output Signals Explained

Several control and data signals work together to produce DRAM output:

- DQ (Data Pins) – Carry the output data

- CAS (Column Address Strobe) – Triggers column access and output timing

- RAS (Row Address Strobe) – Activates the memory row

- CLK (Clock) – Synchronizes output in SDRAM and DDR memory

- OE (Output Enable) – Determines when output drivers are active

DRAM Output vs SRAM Output

| Feature | DRAM Output | SRAM Output |

|---|---|---|

| Speed | Slower | Faster |

| Refresh Required | Yes | No |

| Output Timing | More complex | Simpler |

| Cost per Bit | Lower | Higher |

DRAM output involves extra steps due to charge sensing and refreshing, while SRAM output is faster because it uses flip-flops instead of capacitors.

Why DRAM Output Matters

Understanding DRAM output is important because it directly affects:

- System performance

- Memory latency

- CPU–memory synchronization

- Hardware design and debugging

- Exam and interview questions in computer architecture

Exam-Ready Definition

DRAM output is the data driven onto the memory data bus by a DRAM chip during a read operation, after row and column access timing requirements are satisfied.

Frequently Asked Questions

Is DRAM output always active?

No. DRAM output is only active during a read cycle. At other times, the output pins are in a high-impedance state.

Does DRAM output differ in DDR memory?

Yes. In DDR memory, data output is synchronized to the clock and transferred on both rising and falling edges for higher bandwidth.

Why is DRAM output slower than SRAM?

DRAM must sense tiny capacitor charges and refresh data, adding latency before output becomes valid.

Conclusion

DRAM output is the mechanism by which stored data is delivered from memory to the rest of the system. From timing diagrams to real-world performance, it plays a crucial role in how modern computers function. Whether you’re studying computer networks, system architecture, or hardware design, mastering DRAM output is essential knowledge.